## DESCRIPTION

The ES1869 AudioDrive® solution is a mixed-signal single chip that adds 16-bit stereo sound and FM music synthesis to personal computers. It is compliant with Microsoft® PC 97 and PC 98 specifications and WHQL audio requirements. The ES1869 possesses an embedded microcontroller, OPL3™ superset ESFM™ music synthesizer, 16-bit stereo wave ADC and DAC, 16bit stereo music DAC, MPU-401 UART serial port, dual game port, full Plug and Play support, CD-ROM IDE interface, hardware master volume control, two serial port interfaces to external DSP and external wavetable music synthesizer, I<sup>2</sup>S Zoom Video interface, DMA control logic with FIFO, and ISA bus interface logic. There are three stereo inputs (typically line, CD audio, and auxiliary line) and a mono microphone input. All of this on a single chip that can be designed into a motherboard, add-on card, or integrated into other peripheral cards such as Fax/ Modem, VGA, LAN, I/O, etc.

The ES1869 *Audio*Drive<sup>®</sup> solution can record, compress, and play back voice, sound, and music with built-in mixer controls. It supports full-duplex operation for simultaneous record and playback using two DMA channels. The ESFM<sup>™</sup> synthesizer has extended capabilities within native mode operation providing superior sound and power-down capabilities. It is a register compatible superset of the OPL3 FM synthesizer.

The ES1869 *Audio*Drive<sup>®</sup> solution supports the full ISA Plug and Play standard. It provides Plug and Play configuration for logical devices: audio, ESFM<sup>™</sup> synthesizer, game port, MPU-401, CD-ROM IDE, Modem, and an additional userdefined device.

The MPU-401 serial port is for interfacing to an external MIDI device.

The ES1869 also incorporates **■***Spatializer*<sup>®</sup> VBX<sup>™</sup> technology, provided by Desper Products, Inc., a subsidiary of Spatializer Audio Laboratories, Inc. This processor expands the stereo sound field emitted by two speakers to create a resonant 3-D sound environment.

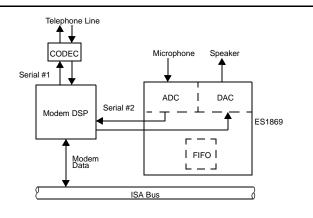

The speakerphone application can be implemented either by digital interface through the DSP serial port, or by analog interface through Mono-In and Mono-Out.

A DSP serial interface in the ES1869 allows an external DSP to take over ADC or DAC resources.

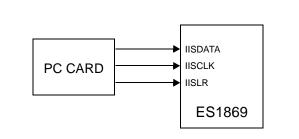

The ES1869 *Audio*Drive<sup>®</sup> solution supports telegaming architecture with headsets and includes data paths for host-based Acoustic Echo Cancellation processing.

Advanced power management features include suspend/ resume from disk or host-independent self-timed powerdown and automatic wake-up. The ES1869 is compliant to the ACPI standard.

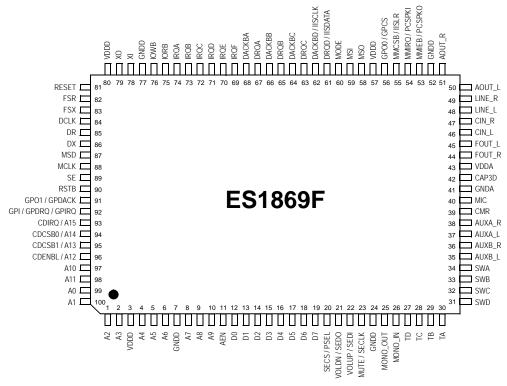

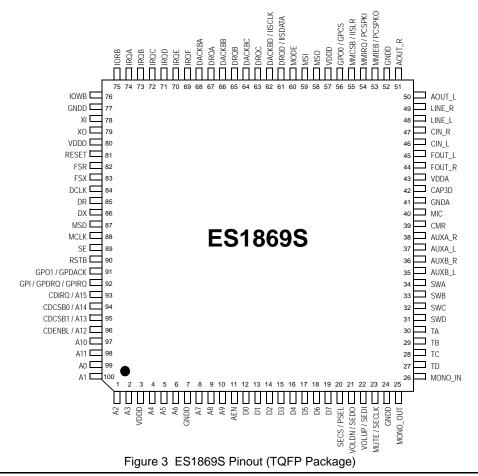

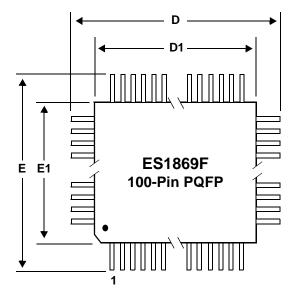

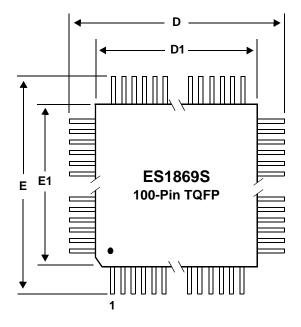

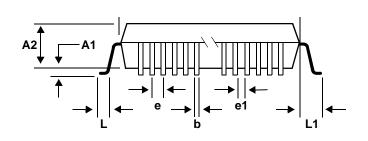

It is available in an industry-standard 100-pin Plastic Quad Flat Pack (PQFP) and Thin Quad Flat Pack (TQFP) packages.

## FEATURES

- Single, high-performance, mixed-signal, 16-bit stereo VLSI chip

- High-quality, OPL3 superset ESFM<sup>™</sup> music synthesizer

- IDE CD-ROM interface

- High-performance DMA supports Demand Transfer and F-type

- Integrated Spatializer® 3-D VBX<sup>™</sup> stereo audio effects technology provided by Desper Products, Inc., a subsidiary of Spatializer Audio Laboratories, Inc.

## Plug and Play Features

- On-chip Plug and Play support for audio, joystick port, FM, Modem, MPU-401, CD-ROM, and a user-defined I/O device

- Software address mapping with software chip select, plus

4 DMA and 6 IRQ selections for motherboard implementation

- Internal configuration data for audio Plug and Play support

- Serial interface for Plug and Play resource EEPROM

### **Record and Playback Features**

- Record, compress, and play back voice, sound, and music

- 16-bit stereo ADC and DAC

- Programmable independent sample rates from 6 kHz to 48.0 kHz for record and playback

- Full-Duplex operation for simultaneous record and playback

- 2- and 3-button hardware volume control for up, down, and mute

## Inputs and Outputs

- Stereo inputs for line-in, auxiliary A (CD audio), and auxiliary B, and a mono input for microphone

- MPU-401 (UART mode) interface for wavetable synthesizers and MIDI devices

FEATURES

- Integrated dual game port

- I<sup>2</sup>S Zoom Video port interface with a sample rate up to 48 kHz for MPEG audio

- Serial port interface to external DSP (e.g. AT&T, TI, API, and MWAVE)

- Separate mono input (MONO\_IN) and mono output (MONO\_OUT\_) for telegaming

## **Mixer Features**

- 7-channel mixer with stereo inputs for line, CD audio, auxiliary line, music synthesizer, digital audio (wave files), and mono inputs for microphone and speakerphone

- Programmable 6-bit logarithmic master volume control

## Power

Advanced power management with self-timed powerdown, automatic wake-up, and suspend/resume to and from disk • Supports 3.3 V or 5.0 V operation

## Compatibility

- Supports PC games and applications for Sound Blaster<sup>™</sup>

and Sound Blaster<sup>™</sup> Pro

- Supports Microsoft Windows<sup>™</sup> Sound System<sup>®</sup>

- Meets PC 97 and PC 98 and WHQL specifications

## **Operating Systems**

- Microsoft Windows®95 and Windows®98

- Microsoft Windows<sup>™</sup> 3.1 and Windows for Workgroups<sup>™</sup>

- Windows Sound System

- Microsoft Windows NT<sup>™</sup> 4.0

- IBM<sup>®</sup> OS/2<sup>®</sup> Warp<sup>™</sup>

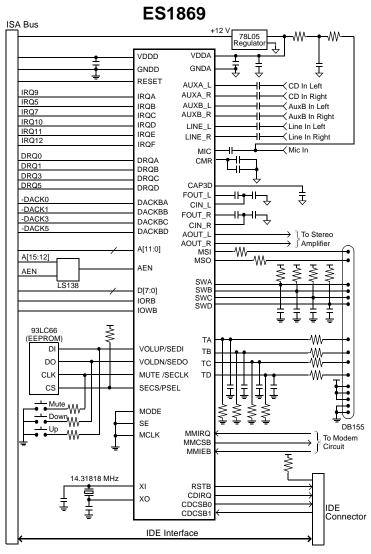

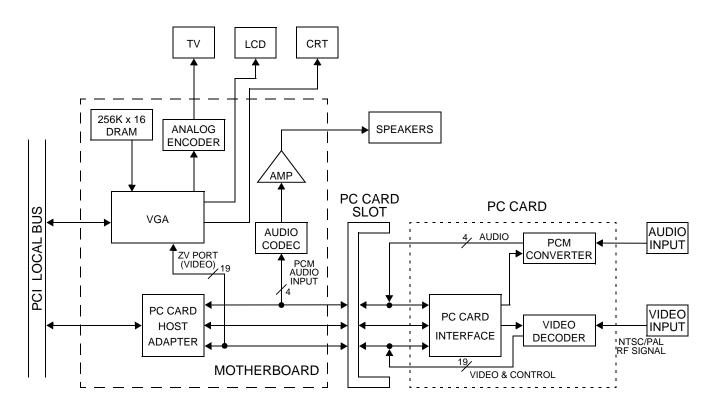

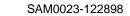

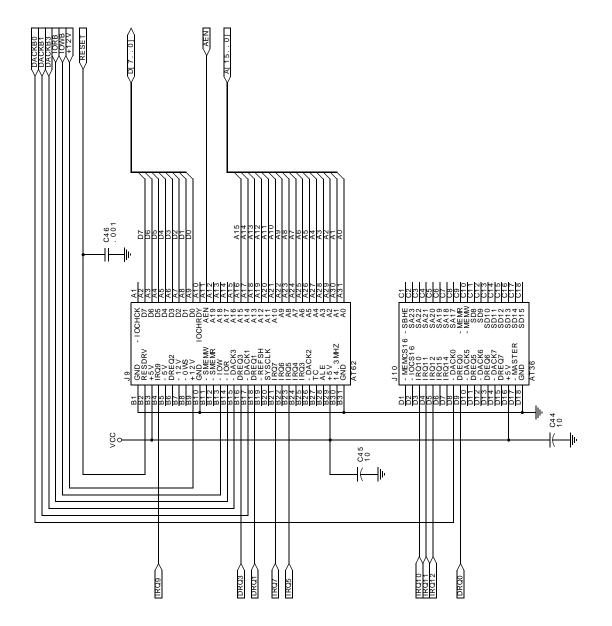

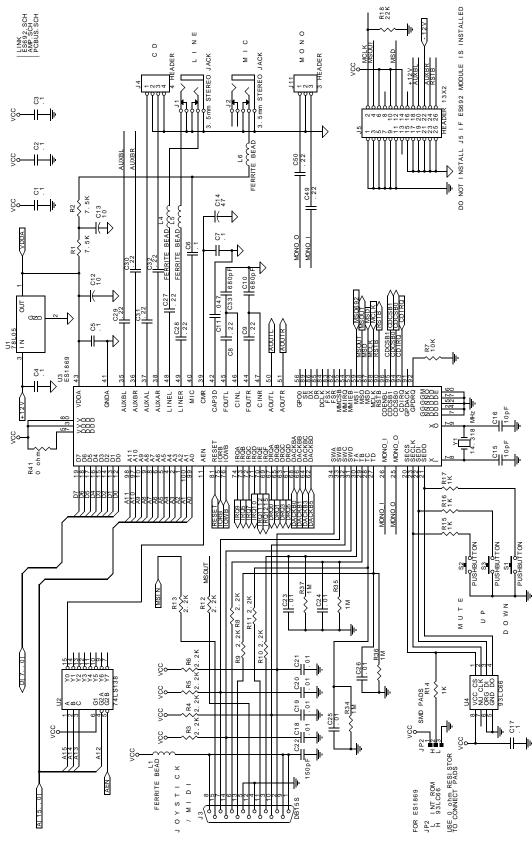

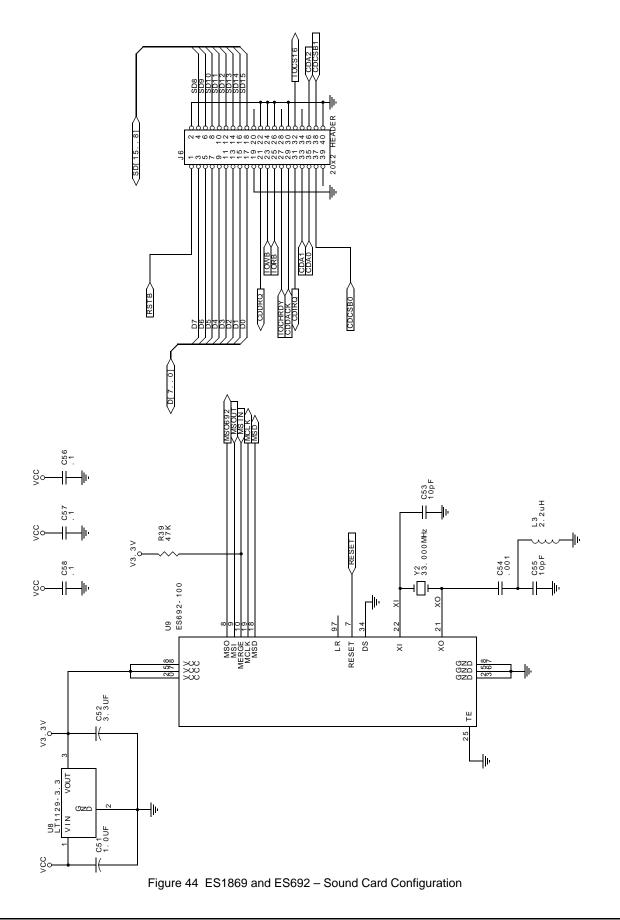

Figure 1 Typical Application

CONTENTS

# CONTENTS

| DESCRIPTION                                     |     |

|-------------------------------------------------|-----|

| FEATURES                                        |     |

| PINOUT                                          | . 5 |

| PIN DESCRIPTION                                 | . 6 |

| FUNCTIONAL DESCRIPTION                          | . 9 |

| Digital Subsystems                              |     |

| Analog Subsystems                               |     |

| MIXER SCHEMATIC BLOCK DIAGRAM                   |     |

|                                                 |     |

| BUS INTERFACING                                 |     |

| DIGITAL AUDIO                                   |     |

| Programming DMA Transfers                       |     |

| Data Formats                                    |     |

| DMA Transfers in Compatibility Mode             | 13  |

| DMA Transfers in Extended Mode                  | 14  |

| Data Transfers Using the Second Audio Channel . |     |

| External DMA Sharing with Audio DMA             |     |

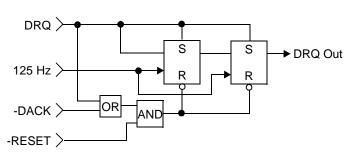

| DRQ Latch Feature                               |     |

|                                                 |     |

| First DMA Channel CODEC                         |     |

| INTERRUPTS                                      |     |

| Interrupt Status Register                       |     |

| Interrupt Mask Register                         |     |

| Sharing Interrupts                              | 18  |

| PERIPHERAL INTERFACING                          | 19  |

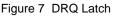

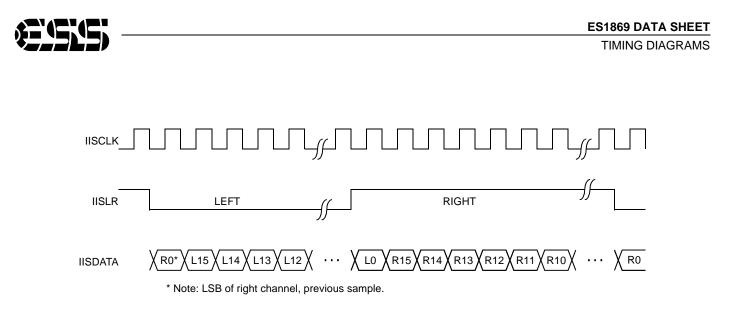

| I <sup>2</sup> S Serial Interface               |     |

| I <sup>2</sup> S Serial Interface Timing        |     |

| Wavetable Interface                             |     |

|                                                 |     |

| DSP Interface                                   |     |

| DSP Operating Modes                             |     |

| Serial Data Format                              |     |

| Modem Interface                                 |     |

| Modem Operating Modes                           | 22  |

| IDE CD-ROM Interface                            | 22  |

| General-Purpose I/O Device                      |     |

| Joystick / MPU-401 Interface                    |     |

| MPU-401 UART Mode                               |     |

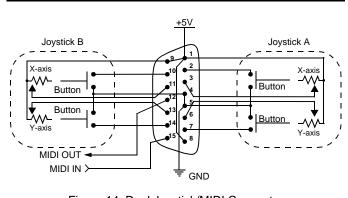

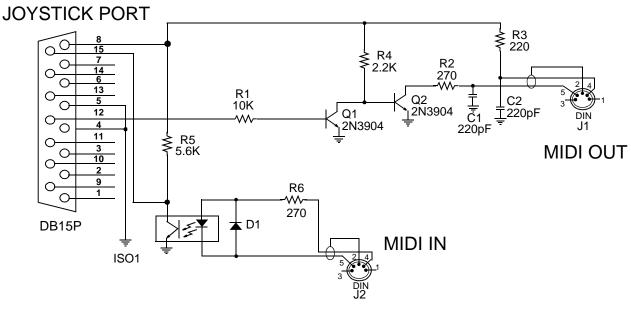

| Joystick / MIDI External Interface              |     |

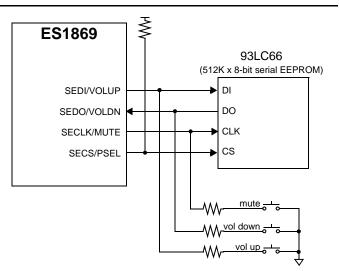

| Serial EEPROM Interface                         |     |

|                                                 |     |

| EEPROM ROM Format                               |     |

| MONO_IN and MONO_OUT                            |     |

| Spatializer® VBX <sup>™</sup> Audio Processor   |     |

| Hardware and Master Volume Control              |     |

| PC Speaker                                      |     |

| PC Speaker Volume Control                       | 26  |

| ANALOG DESIGN CONSIDERATIONS                    | 27  |

| Game Port                                       | 27  |

| Reference Generator                             |     |

| Switch-Capacitor Filter                         |     |

| Audio Inputs and Outputs                        |     |

| PNP CONFIGURATION AND REGISTERS                 |     |

|                                                 |     |

| Access to PnP Registers                         |     |

| Configuration Ports                             |     |

| Bypass Key                                      |     |

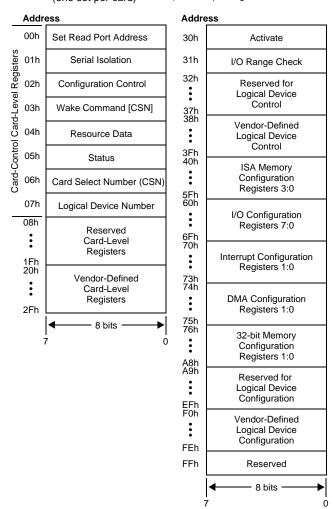

| Card-Control Card-Level Registers (00h-07h)     |     |

| Vendor-Defined Card-Level Registers (20h-29h)   | 30  |

| Logical Device Registers                        |     |

| LDN 0: Configuration Device                     | 32  |

|                                                 |     |

| LDN 2: Joystick Device                          |     |

| LDN 3: MPU-401 Device                           |     |

|                                                 | 54  |

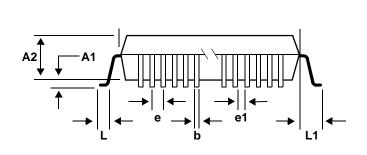

| Pop Prevention in the External Amplifier.77Power Management and the FM Synthesizer.78Self-Timed Power-Down.78Enabling Self-Timed Power-Down.78General-Purpose Outputs and Power-Down.78ELECTRICAL CHARACTERISTICS.79Absolute Maximum Ratings.79Thermal Characteristics.79Operating Conditions.79Operating Current.79TIMING DIAGRAMS.80TIMING CHARACTERISTICS.85MECHANICAL DIMENSIONS.86                                                                                                                                                                                                                                                                                                                                                                                                                          | ES1869F PQFP Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

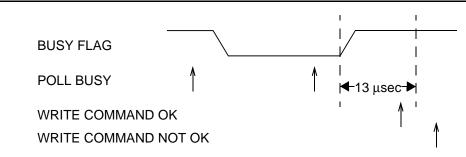

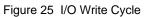

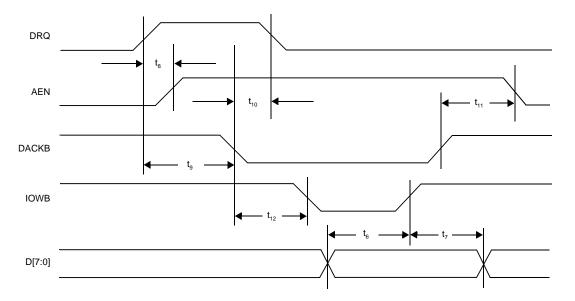

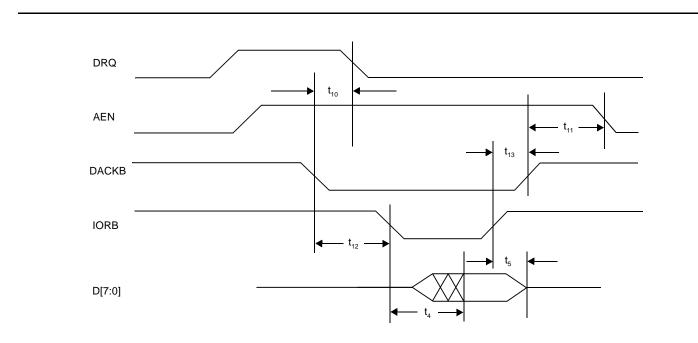

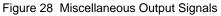

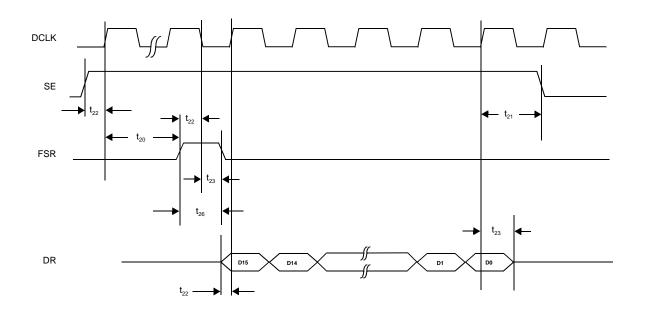

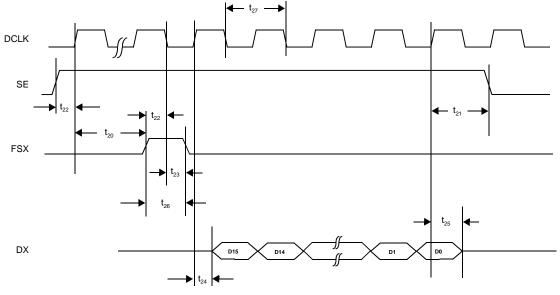

| FIGURESFigure 1 Typical Application.2Figure 2 ES1869F Pinout (PQFP Package).5Figure 3 ES1869S Pinout (TQFP Package).5Figure 4 ES1869 Block Diagram.9Figure 5 ES1869 Mixer Schematic Block Diagram.11Figure 6 Data Transfer Modes.13Figure 7 DRQ Latch.15Figure 9 Telegaming Mode.20Figure 10 Default Mode.20Figure 11 16-Bit Data, Positive Sync Pulse.21Figure 12 Speakerphone or Modern w/ Voice-Over-Data.22Figure 13 IDE Interface – Typical Application.22Figure 16 Serial EEPROM – Typical Application.24Figure 17 PC Speaker Volume Circuitry.26Figure 18 Reference Generator Pin Diagram.27Figure 20 Configuration Register Set.28Figure 21 Command Transfer Timing.45Figure 22 Summary of Power States in the ES1869.75Figure 23 Reset Timing.80Figure 24 I/O Read Cycle.80Figure 25 I/O Write Cycle.80 | Figure 26Compatibility Mode DMA Write Cycle81Figure 27Compatibility Mode DMA Read Cycle81Figure 28Miscellaneous Output Signals82Figure 29Serial Mode Receive Operation82Figure 30Serial Mode Transmit Operation83Figure 31Serial Input Timing for I2S Interface83Figure 32I2S Digital Input Format with 16 SCLK Periods84Figure 33ES1869F PQFP Mechanical Dimensions86Figure 34ES1869S TQFP Mechanical Dimensions87Figure 35Example ZV Port Implementation93Figure 36Typical ZV Port Audio Implementation94Figure 37Audio Interface Timing95Figure 38I2S Digital Input Format with 16 SCLK periods96Figure 39ES1869 – Motherboard Configuration98Figure 40ES1869 and ES692 – Motherboard Configuration99Figure 41Amplifier – Motherboard Configuration100Figure 43ES1869 – Sound Card Configuration104Figure 44ES1869 and ES692 – Sound Card Configuration104Figure 45Amplifier – Sound Card Configuration106Figure 46PC Interface – Sound Card Configuration107Figure 47Analog Components on One Side of the PCB110Figure 48Analog Components on Both Sides of the PCB110 |

## TABLES

4

| Table 1    ISA Bus Interface Pins    12                      |

|--------------------------------------------------------------|

| Table 2 Extended Mode Audio 1 Controller Registers   14      |

| Table 3 Audio 2 Related Mixer Registers    15                |

| Table 4    ES1869 Interrupt Sources                          |

| Table 5 Interrupt Status Bits in Config_Base+6h              |

| Table 6    I²S Interface Pins    19                          |

| Table 7    Wavetable Interface Pins    19                    |

| Table 8 DSP Interface Pins    19                             |

| Table 9 External Modem Interface Pins                        |

| Table 10    IDE CD-ROM Interface Pins    22                  |

| Table 11 Logical Device Summary                              |

| Table 12 I/O Ports for Configuration, Audio, FM, MPU-401,    |

| and Joystick Devices                                         |

| Table 13 Comparison of Operation Modes                       |

| Table 14 Uncompressed DAC Transfer Modes    46               |

| Table 15    Uncompressed ADC Transfer Modes                  |

| Table 16 Command Sequences for DMA Playback                  |

| Table 17 Command Sequence for DMA Record    50               |

| Table 18         Sound Blaster Pro/Extended Access Registers |

| Table 19 | SB Pro Read Volume Emulation                    |

|----------|-------------------------------------------------|

| Table 20 | SB Pro Write Volume Emulation 54                |

| Table 21 | Extended Access Mixer Volume Values 55          |

| Table 22 | Mixer Input Volume Registers 55                 |

|          | Sound Blaster Compatibility Register Summary 56 |

| Table 24 | ESS Mixer Registers Summary 57                  |

| Table 25 | ESS Controller Registers Summary 67             |

| Table 26 | Command Summary 72                              |

| Table 27 | Digital Characteristics                         |

| Table 28 | Analog Characteristics                          |

| Table 29 | Timing Characteristics 85                       |

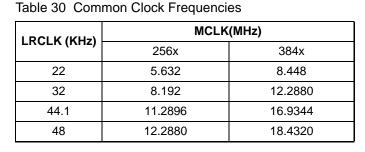

| Table 30 | Common Clock Frequencies 94                     |

| Table 31 | AC Parameters for Audio Signals 95              |

| Table 32 | ZV Port Interface Pin Assignments               |

| Table 33 | ES1869 Motherboard Bill of Materials (BOM) 102  |

| Table 34 | ES1869 Sound Card Bill of Materials (BOM) 108   |

|          |                                                 |

PINOUT

## PINOUT

## **PIN DESCRIPTION**

| Name     | Number                        | I/O | Description                                                                                                                                                                                                                                                                                                           |  |

|----------|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A[11:0]  | 99,100,1,2,6:4,<br>10:8,97,98 | I   | Address inputs from the ISA bus.                                                                                                                                                                                                                                                                                      |  |

| VDDD     | 3,57,80                       | I   | Digital supply voltage (5 V ± 10%).                                                                                                                                                                                                                                                                                   |  |

| GNDD     | 7,24,52,77                    | Ι   | Digital ground.                                                                                                                                                                                                                                                                                                       |  |

| AEN      | 11                            | I   | Active-low address enable from the ISA bus.                                                                                                                                                                                                                                                                           |  |

| D[7:0]   | 19:12                         | I/O | ISA bidirectional data bus.                                                                                                                                                                                                                                                                                           |  |

| PSEL     | 20                            | Ι   | Selects the PnP ROM device used:0Internal ROM193LC66 - 512 x 8, 9 address bits                                                                                                                                                                                                                                        |  |

| SECS     |                               | I/O | Serial EEPROM CS. This is an input pin during RESET.                                                                                                                                                                                                                                                                  |  |

| SEDO     | 21                            | Ι   | Input connected to the data output pin of the external PnP serial EEPROM.                                                                                                                                                                                                                                             |  |

| VOLDN    | 21                            | I   | Active-low volume decrease button input with internal pull-up (shared with the SEDO pin).                                                                                                                                                                                                                             |  |

| SEDI     | 22                            | 0   | Output connected to the data input pin of the external PnP serial EEPROM.                                                                                                                                                                                                                                             |  |

| VOLUP    | 22                            | Ι   | Active-low volume increase button input with internal pull-up (shared with the SEDI pin).                                                                                                                                                                                                                             |  |

| MUTE     | 22                            | Ι   | Active-low mute toggle button input with internal pull-up (shared with the SECLK pin).                                                                                                                                                                                                                                |  |

| SECLK    | 23                            | 0   | External serial EEPROM clock output for PnP.                                                                                                                                                                                                                                                                          |  |

| MONO_OUT | 25                            | 0   | Mono output with source select and volume control (including mute). This pin can drive an external 5k ohm AC load.                                                                                                                                                                                                    |  |

| MONO_IN  | 26                            | Ι   | Mono input to mixer and ADC. This pin has an internal pull-up to CMR.                                                                                                                                                                                                                                                 |  |

| T(A-D)   | 27:30                         | I/O | Joystick timer pins. These pins connect to the X-Y positioning variable resistors for the two joysticks.                                                                                                                                                                                                              |  |

| SW(A-D)  | 31:34                         | Ι   | Active-low joystick switch setting inputs. These pins have an internal pull-up resistor. The joystick port is typically at address 201h.                                                                                                                                                                              |  |

| AUXB_L   | 35                            | Ι   | Auxiliary B input left. AUXB_L has an internal pull-up resistor to CMR. Normally intended for connection to an external music synthesizer or other line-level source.                                                                                                                                                 |  |

| AUXB_R   | 36                            | I   | Auxiliary B input right. AUXB_R has an internal pull-up resistor to CMR. Normally intended for connection to an external music synthesizer or other line-level source.                                                                                                                                                |  |

| AUXA_L   | 37                            | I   | Auxiliary A input left. AUXA_L has an internal pull-up resistor to CMR. Normally intended for connection to an internal or external CD-ROM analog output.                                                                                                                                                             |  |

| AUXA_R   | 38                            | Ι   | Auxiliary A input right. AUXA_R has an internal pull-up resistor to CMR. Normally intended for connection to an internal or external CD-ROM analog output.                                                                                                                                                            |  |

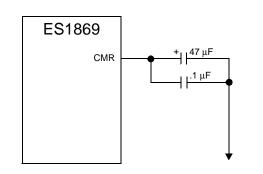

| CMR      | 39                            | 0   | Common mode buffered reference output (2.25 V $\pm$ 5%). This pin should be bypassed to analog ground with a 47 $\mu$ F electrolytic capacitor with a 0.1 $\mu$ F capacitor in parallel.                                                                                                                              |  |

| MIC      | 40                            | Ι   | Microphone input. MIC has an internal pull-up resistor to CMR.                                                                                                                                                                                                                                                        |  |

| GNDA     | 41                            | Ι   | Analog ground.                                                                                                                                                                                                                                                                                                        |  |

| CAP3D    | 42                            | Ι   | Bypass capacitor to analog ground for 3-D effects.                                                                                                                                                                                                                                                                    |  |

| VDDA     | 43                            | Ι   | Analog supply voltage (5 V $\pm$ 5%). Must be greater than or equal to VDDD - 0.3 V.                                                                                                                                                                                                                                  |  |

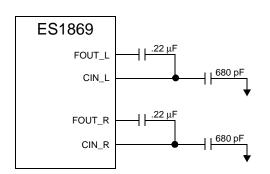

| FOUT_R   | 44                            | 0   | Filter output right. FOUT_R is AC-coupled externally to CIN_R to remove DC offsets. This output has an internal series resistor of about 5k ohms. A capacitor to analog ground on this pin can be used to create a low-pass filter pole that removes the switching noise introduced by the switched-capacitor filter. |  |

PIN DESCRIPTION

| Name                | Number     | I/O | Description                                                                                                                                                                                                                                                                                                                                          |  |  |

|---------------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FOUT_L              | 45         | 0   | Filter output left. FOUT_L is AC-coupled externally to CIN_L to remove DC offsets. This output has an internal series resistor of about 5k ohms. A capacitor to analog ground on this pin can be used to create a low-pass filter pole that removes the switching noise introduced by the switched-capacitor filter.                                 |  |  |

| CIN_L               | 46         | Ι   | Capacitive coupled input left. CIN_L has an internal pull-up resistor to CMR of approxi-<br>mately 50k ohms.                                                                                                                                                                                                                                         |  |  |

| CIN_R               | 47         | Ι   | Capacitive coupled input right. CIN_R has an internal pull-up resistor to CMR of approxi-<br>mately 50k ohms.                                                                                                                                                                                                                                        |  |  |

| LINE_L              | 48         | Ι   | Line input left. LINE_L has an internal pull-up resistor to CMR.                                                                                                                                                                                                                                                                                     |  |  |

| LINE_R              | 49         | I   | Line input right. LINE_R has an internal pull-up resistor to CMR.                                                                                                                                                                                                                                                                                    |  |  |

| AOUT_L              | 50         | 0   | Line-level stereo output left. AOUT_L can drive a 10k ohm load.                                                                                                                                                                                                                                                                                      |  |  |

| AOUT_R              | 51         | 0   | Line-level stereo output right. AOUT_R can drive a 10k ohm load.                                                                                                                                                                                                                                                                                     |  |  |

| MMIEB °             |            | Ι   | Modem interrupt enable active-low input. Generated from the modem UART.                                                                                                                                                                                                                                                                              |  |  |

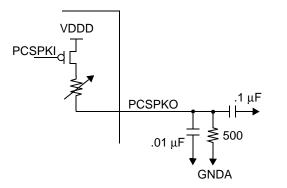

| PCSPKO <sup>1</sup> | 53         | 0   | PC speaker analog output.                                                                                                                                                                                                                                                                                                                            |  |  |

| MMIRQ º             | <b>F</b> 4 | I   | Modem interrupt request active-high input. IRQ input from the modem device gets mapped to an IRQ output on the ES1869 based on the PnP configuration.                                                                                                                                                                                                |  |  |

| PCSPKI 1            | 54         | Ι   | Normally low digital PC speaker input. This signal is converted to an analog signal with volume control and appears on analog output PCSPKO.                                                                                                                                                                                                         |  |  |

| IISLR 1             |            | Ι   | Left/right strobe for I <sup>2</sup> S interface. This pin has a pull-down.                                                                                                                                                                                                                                                                          |  |  |

| MMCSB º             | 55         | 0   | Output from ES1869 for the modem CSB. The address space is determined by the PnP configuration.                                                                                                                                                                                                                                                      |  |  |

| GPCS                | 56         | 0   | If selected by the PnP logic, GPCS is an active-high user-defined chip select for an external general-purpose device.                                                                                                                                                                                                                                |  |  |

| GPO0                | 50         | 0   | Output that is set low by external reset and is thereafter controlled by bit 0 of port<br>Audio_Base+7h. Available to system software for power management or other applications.                                                                                                                                                                    |  |  |

| MSO                 | 58         | 0   | MIDI serial data output.                                                                                                                                                                                                                                                                                                                             |  |  |

| MSI                 | 59         | Ι   | MIDI serial data input. Schmitt trigger input with internal pull-up resistor. Either MPU-401 or Sound Blaster formats.                                                                                                                                                                                                                               |  |  |

| MODE                | 60         | Ι   | Mode function pin. Connect to either GNDD or VDDD to select the function of the groups of multiple function pins (indicated by a superscript 0 or 1).                                                                                                                                                                                                |  |  |

| DRQD º              | 04         | 0   | Tri-state output. Optional 16-bit DMA request for IDE interface.                                                                                                                                                                                                                                                                                     |  |  |

| IISDATA 1           | 61         | Ι   | Serial data for I <sup>2</sup> S interface. This pin has a pull-down.                                                                                                                                                                                                                                                                                |  |  |

| DACKBD 0            |            | Ι   | Optional 16-bit DMA acknowledge for IDE interface.                                                                                                                                                                                                                                                                                                   |  |  |

| IISCLK 1            | 62         | Ι   | Serial shift clock for I <sup>2</sup> S interface. This pin has a pull-down.                                                                                                                                                                                                                                                                         |  |  |

| DRQ(A-C)            | 67,65,63   | 0   | Three (A,B,C) active-high DMA requests to the ISA bus. Unselected DRQ outputs are high impedance. When DMA is not active, the selected DRQ output has a pull-down device that holds the DRQ line inactive unless another device that shares the same DRQ line can source enough current to make the DRQ line active. DRQs are software configurable. |  |  |

| DACKB(A-C)          | 68,66,64   | Ι   | Three (A,B,C) active-low DMA acknowledge inputs.                                                                                                                                                                                                                                                                                                     |  |  |

| IRQ(A-F)            | 69:74      | 0   | Six (A,B,C,D,E,F) active-high interrupt requests to the ISA bus. Unselected IRQ outputs are high impedance. IRQs are software configurable.                                                                                                                                                                                                          |  |  |

| IORB                | 75         | I   | Active-low read strobe from the ISA bus.                                                                                                                                                                                                                                                                                                             |  |  |

| IOWB                | 76         | I   | Active-low write strobe from the ISA bus.                                                                                                                                                                                                                                                                                                            |  |  |

| XI                  | 78         | Ι   | Crystal oscillator/external clock input. Connect to external 14.318 MHz crystal or clock source with CMOS levels.                                                                                                                                                                                                                                    |  |  |

**PIN DESCRIPTION**

| Name             | Number | I/O | Description                                                                                                                                                                                                                                                       |  |

|------------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ХО               | 79     | 0   | Crystal oscillator output. Connect to external 14.318 MHz crystal.                                                                                                                                                                                                |  |

| RESET            | 81     | I   | Active-high reset from the ISA bus.                                                                                                                                                                                                                               |  |

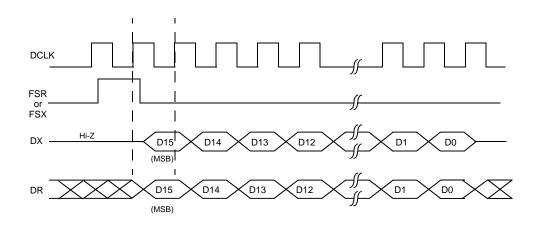

| FSR              | 82     | I   | Input with internal pull-down. Frame sync for receive data from external DSP. Programma-<br>ble for active-high or active-low.                                                                                                                                    |  |

| FSX              | 83     | I   | Input with internal pull-down. Frame sync for transmit request from external DSP. Program-<br>mable for active-high or active-low.                                                                                                                                |  |

| DCLK             | 84     | Ι   | Input with internal pull-down. Serial data clock from external DSP. Typically 2.048 MHz.                                                                                                                                                                          |  |

| DR               | 85     | I   | Input with internal pull-down. Data receive pin from external DSP.                                                                                                                                                                                                |  |

| DX               | 86     | 0   | Tri-state output. Data transmit to external DSP. High impedance when not transmitting.                                                                                                                                                                            |  |

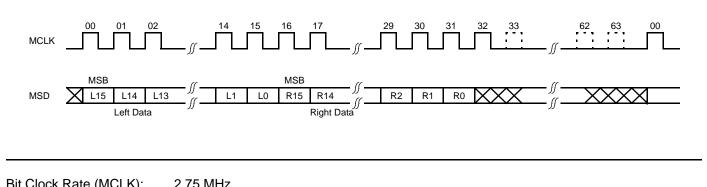

| MSD              | 87     | I   | Input with internal pull-down. Music serial data from external ES689/ES69x wavetable music synthesizer.                                                                                                                                                           |  |

| MCLK             | 88     | I   | Input with internal pull-down. Music serial clock from external ES689/ES69x wavetable music synthesizer.                                                                                                                                                          |  |

| SE               | 89     | I   | Input with internal pull-down. Active-high to enable serial mode, that is, it enables an exter-<br>nal DSP to control analog resources of the ES1869 through the DSP serial interface. This<br>pin is logically OR'd internally with bit 7 of mixer register 48h. |  |

| RSTB             | 90     | 0   | Inverted RESET output.                                                                                                                                                                                                                                            |  |

| GPDACK           |        | 0   | Active-low DMA acknowledge output to general-purpose device that uses DMA.                                                                                                                                                                                        |  |

| GPO1             | 91     | 0   | Output that is set high by external reset and thereafter controlled by bit 1 of port<br>Audio_Base+7h. Available to system software for power management or other applications.                                                                                   |  |

| GPDRQ            |        | Ι   | DMA request output from general-purpose device based on the PnP configuration.                                                                                                                                                                                    |  |

| GPI              | 92     | I   | General-purpose input option.                                                                                                                                                                                                                                     |  |

| GPIRQ            |        | Ι   | Interrupt request output from the general-purpose device based on the PnP configuration.                                                                                                                                                                          |  |

| A15 <sup>1</sup> | 93     | Ι   | Address input from the ISA bus.                                                                                                                                                                                                                                   |  |

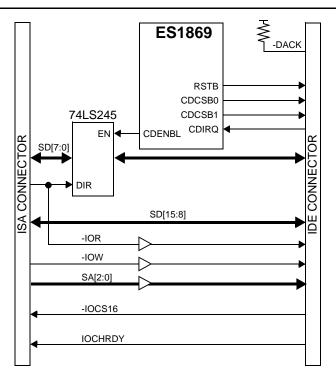

| CDIRQ 0          | 93     | I   | Interrupt request input from the IDE interface.                                                                                                                                                                                                                   |  |

| A14 <sup>1</sup> | 0.4    | I   | Address input from the ISA bus.                                                                                                                                                                                                                                   |  |

| CDCSB0 º         | 94     | 0   | Active-low IDE interface chip select #0.                                                                                                                                                                                                                          |  |

| A13 <sup>1</sup> | 05     | I   | Address input from the ISA bus.                                                                                                                                                                                                                                   |  |

| CDCSB1 º         | 95     | 0   | Active-low IDE interface chip select #1.                                                                                                                                                                                                                          |  |

| A12 <sup>1</sup> | 06     | Ι   | Address input from the ISA bus.                                                                                                                                                                                                                                   |  |

| CDENBL 0         | 96     | 0   | Active-low IDE data bus transceiver enable.                                                                                                                                                                                                                       |  |

0: Pins enabled by MODE = 0 (pin 60). 1: Pins enabled by MODE = 1 (pin 60).

FUNCTIONAL DESCRIPTION

## FUNCTIONAL DESCRIPTION

This section shows the overall structure of the ES1869 and discusses its major functional subunits.

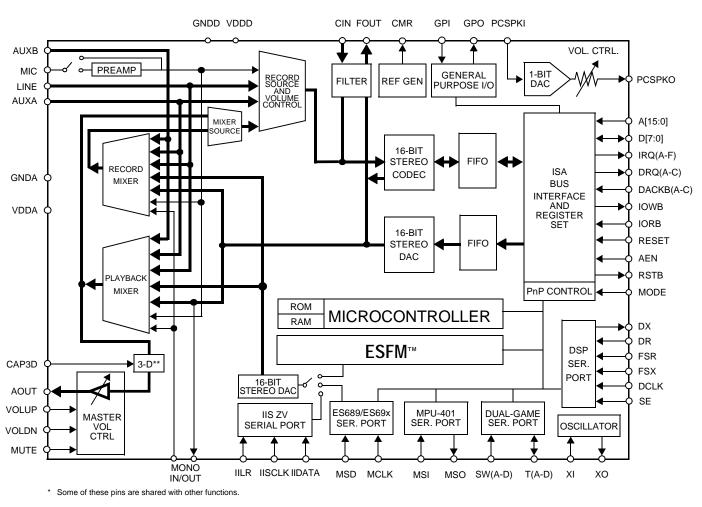

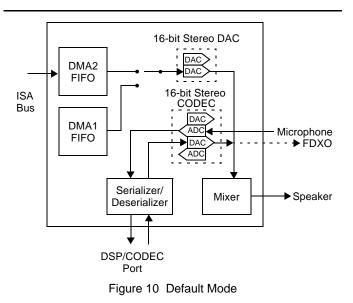

The major subunits of the ES1869 are shown in Figure 4 and described briefly in the following paragraphs.

<sup>\*\* 3-</sup>D Processor uses Spatializer <sup>©</sup> VBX<sup>™</sup> 3-D technology provided by Desper Products, Inc., a subsidiary of Spatializer Audio Laboratories, Inc.

Figure 4 ES1869 Block Diagram

## **Digital Subsystems**

- **RISC microcontroller** game-compatible audio functions are performed by an embedded microcontroller.

- **Oscillator** circuitry to support an external crystal.

- **ROM and RAM** firmware ROM and data RAM to the embedded microcontroller.

- **FIFO** RAM for a 256-byte FIFO data buffer for use with the first audio channel and RAM for a 64-byte FIFO data buffer for use with the second audio channel.

- **ISA bus interface** provides interface to ISA bus address, data, and control signals.

- **Dual game port** integrated dual game port for two joysticks.

- MPU-401 serial port asynchronous serial port for MIDI devices such as a wavetable synthesizer or a music keyboard input.

- Wavetable serial port serial port connection from the output of an ES689 or ES69x that eliminates the requirements for an external DAC.

- **DSP serial port** interface to an optional external DSP for control of the CODEC.

- I<sup>2</sup>S Zoom Video interface supports sample rates up to 48 kHz for MPEG audio.

- **ESFM music synthesizer** high-quality, OPL3 superset FM synthesizer with 20 voices.

- Hardware volume control 3 pushbutton inputs with internal pull-up devices for up/down/mute that can be used to adjust the master volume control.

A software-selectable option allows the mute input to be omitted. The mute input is defined as the state when both up and down inputs are low. By default, this feature is disabled.

## Analog Subsystems

- Record and Playback Mixers seven input stereo mixers. Each input has independent left and right 4-bit volume control:

- Line In

- Mic In

- Aux A (CD-audio)

- Aux B (or FDXI)

- Digitized audio (wave files)

- FM / ES689/ES69x / I2S ZV music DAC

- MONO\_IN/MONO\_OUT

- 16-Bit stereo CODEC for audio record and playback of the first audio channel.

- **16-Bit stereo system DAC** for audio playback of the second audio channel.

- **16-Bit stereo music DAC** for ESFM<sup>™</sup>, external wavetable synthesizer, or IIS MPEG audio.

- 1-Bit DAC for PC speaker digital input.

- 3-D Processor a 3-D processor using Spatializer<sup>®</sup> VBX<sup>™</sup> stereo 3-D audio effects technology, provided by Desper Products, Inc., a subsidiary of Spatializer Audio Laboratories, Inc.

- Record source and input volume control input source and volume control for recording. The recording source can be selected from one of four choices:

- Line In

- Mic In

- Aux A (CD-audio)

- Mixer (playback or record)

- **Mixer source** determines which mixer is used for the record source, either the playback or record mixer.

- Output volume and mute control The master volume is controlled either by programmed I/O or by volume control switch inputs. The master volume supports 6 bits per channel plus mute.

- Reference generator analog reference voltage generator.

- PC speaker volume control The PC speaker is supported with a 1-bit DAC with volume control. The analog output pin PCSPKO is intended to be externally mixed at the external amplifier.

- Filter switched capacitor low-pass filter.

- General purpose I/O outputs available to system software for power management or other applications.

- Pre-amp 26 dB microphone pre-amplifier.

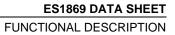

## MIXER SCHEMATIC BLOCK DIAGRAM

Figure 5 ES1869 Mixer Schematic Block Diagram

## **BUS INTERFACING**

This section discusses interfacing to the PC bus, and items relating to configuration for the bus.

Table 1 shows the pins used to interface the ES1869 to the ISA bus.

Table 1 ISA Bus Interface Pins

| Pins       | Descriptions                                                                                                                                                                                                                                                                                                                                           |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[15:12]   | Dual-purpose pins. A[15:12] are ISA bus address inputs.                                                                                                                                                                                                                                                                                                |

| A[11:0]    | ISA bus address inputs.                                                                                                                                                                                                                                                                                                                                |

| AEN        | ISA active-low address enable.                                                                                                                                                                                                                                                                                                                         |

| D[7:0]     | ISA bidirectional data bus.                                                                                                                                                                                                                                                                                                                            |

| DRQD       | Dual-purpose pin. DRQD is a tri-state output. Optional 16-bit DMA request for IDE interface.                                                                                                                                                                                                                                                           |

| DACKBD     | Dual-purpose pin. DACKBD is an optional 16-bit DMA acknowledge for IDE interface.                                                                                                                                                                                                                                                                      |

| DRQ(A-C)   | Three (A, B, C) active-high DMA requests to the ISA bus. Unselected DRQ outputs are high-impedance. When DMA is not active, the selected DRQ output has a pull-down device that holds the DRQ line inactive unless another device that shares the same DRQ line can source enough current to make the DRQ line active. DRQs are software configurable. |

| DACKB(A-C) | Three (A, B, C) active-low DMA acknowledge inputs.                                                                                                                                                                                                                                                                                                     |

| IRQ(A-F)   | Six (A, B, C, D, E, F) active-high interrupt requests to the ISA bus. Unselected IRQ outputs are high-impedance. IRQs are software configurable.                                                                                                                                                                                                       |

| IORB       | ISA active-low read strobe.                                                                                                                                                                                                                                                                                                                            |

| IOWB       | ISA active-low write strobe.                                                                                                                                                                                                                                                                                                                           |

| RESET      | Active-high. Reset from ISA bus.                                                                                                                                                                                                                                                                                                                       |

12

DIGITAL AUDIO

## **DIGITAL AUDIO**

The ES1869 incorporates two digital audio channels. There are three sources of DMA requests and three targets for DMA acknowledge:

- Audio 1 The first audio channel. This channel is used for Sound Blaster Pro compatible DMA, Extended mode DMA, and programmed I/O. It can be used for either record or playback. Ideally, this channel should be assigned to ISA channel 1.

- Audio 2 The second audio channel. This channel is used for audio playback in full-duplex mode. This channel can be mapped to any of the three 8-bit ISA DMA channels: 0,1, or 3.

- External GPO1 can be assigned to be a DMA acknowledge output, GPI can be used as a DMA request input from an external device; either CD-ROM, Modem, or general-purpose device. This channel can be mapped to any of the four DRQ/DACK pairs.

The three DMA sources are mapped to the four DMA pin pairs by Plug and Play (PnP) registers. Also, the four DMA pin pairs are assigned ISA DMA channel numbers by Vendor-Defined Card-Level registers 23h and 24h. At least two of the four pin pairs must be assigned to 8-bit ISA DMA channels (0,1, or 3). The other one or two of the four pin pairs can be assigned to one of the 16-bit ISA DMA channels (5, 6, or 7) for use by the external DMA source.

In order for a DRQ output pin to be *driving* (as opposed to *high-impedance*), two conditions must be met:

- The PnP register for the DMA of a given device must match the ISA DMA channel number of the pin.

- The given device must be activated; that is, bit 0 of PnP register 30h must be high.

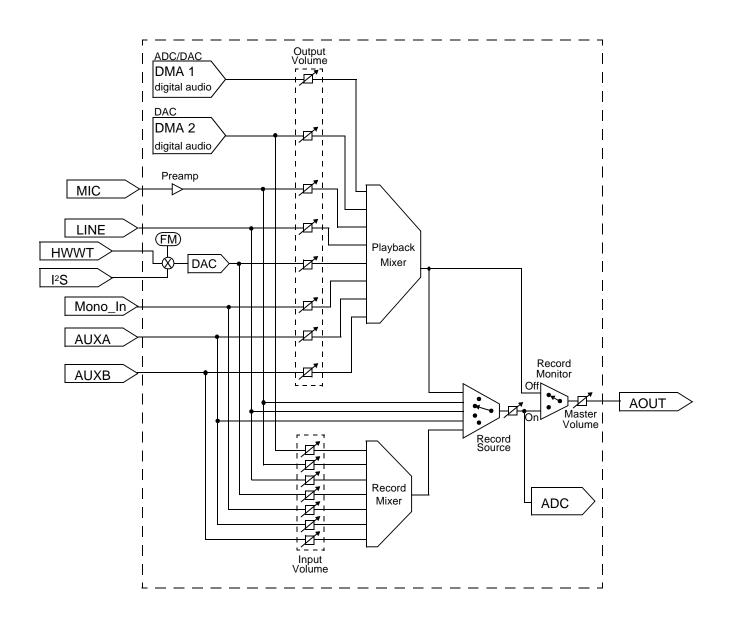

Figure 6 Data Transfer Modes

## Programming DMA Transfers

Programming data transfers can be complicated with the ES1869. Both Compatibility and Extended modes offer a variety of modes for conducting transfers. The commands

to enable the different transfers vary depending on which DMA channel and which mode (Compatibility or Extended) is used.

The biggest difference in available data transfer modes is between audio channel 1 and audio channel 2. This is illustrated in Figure 6. Audio 2 only allows for DMA mode. Audio 1 allows for Direct mode and DMA mode when using Compatibility mode, and for programmed I/O and DMA mode when using Extended mode.

## **Data Formats**

See "Data Formats" on page 44.

### DMA Transfers in Compatibility Mode

The first audio channel is programmed using standard Sound Blaster compatible commands. These commands are written to the chip through port Audio\_Base+Ch.

When programming the first audio channel for transfers, one of the following modes can be used:

- Direct mode

- DMA modes

- Normal

- Auto-Initialize

In addition, both DMA Normal mode and DMA Auto-Initialize mode can use a special High-Speed mode.

### **Direct Mode**

In Direct mode, timing for DMA transfers is handled by the application program. For example, the system timer can be reprogrammed to generate interrupts at the desired sample rate. At each system timer interrupt, the command 10h, 11h, 20h, or 21h is issued followed by the sample. Polling of the Write-Buffer-Available flag (Audio\_Base+Ch [bit 7]) is required before writing the command and between writing the command and the data.

**NOTE:** The switched capacitor filter is initialized by reset for an intended sample rate of 8 kHz. In Direct mode, the application may wish to adjust this filter appropriate to the actual sample rate. Do this by programming the timer with command 40h just as if the application were using DMA mode.

## DMA Modes

In DMA mode, the programmable timer in the ES1869 controls the rate at which samples are sent to the CODEC. The timer is programmed using command 40h, which also sets up the programmable filters inside the ES1869. The ES1869 firmware maintains an internal FIFO (32 levels for 16-bit transfers, 64 levels for 8-bit transfers) that is filled by DMA transfers and emptied by timed transfers to the DAC.

Before a DMA transfer, the application first programs the DMA controller for the desired transfer size and address, then programs the ES1869 with the same size information. At the end of the transfer, the ES1869 generates an interrupt request, indicating that the current block transfer is complete. The FIFO gives the application program sufficient time to respond to the interrupt and initiate the next block transfer.

The ES1869 supports both Normal DMA mode and Auto-Initialize DMA mode.

### Normal DMA Mode

In Normal mode DMA transfers, the DMA controller must be initialized and the ES1869 commanded for every block that is transferred.

### Auto-Initialize DMA Mode

In Auto-Initialize mode, the DMA transfer is continuous, in a circular buffer, and the ES1869 generates an interrupt for the transition between buffer halves. In this mode the DMA controller and ES1869 only need to be set up once.

### High-Speed Mode

The ES1869 supports mono 8-bit DMA transfers at a rate up to 44 kHz. Mono 16-bit transfers are supported up to a rate of 22 kHz.

The special "High-Speed mode" allows 8-bit sampling up to 44 kHz for ADC, using commands 98h (auto-initialize) and 99h (normal). No automatic gain control (AGC) is performed. The input volume is controlled with command DDh.

## DMA Transfers in Extended Mode

The first audio channel is programmed using the controller registers internal to the ES1869. The commands written to the controller registers are written to the chip through port Audio\_Base+Ch.

When programming the first audio channel for transfers, one of the following modes can be used:

- Programmed I/O

- DMA modes

- Normal (Single or Demand transfer)

- Auto-Initialize (Single or Demand transfer)

In addition, both DMA normal mode and DMA autoinitialize mode use Single transfer or Demand transfer modes.

### Programmed I/O

For some applications, DMA mode is not suitable or available for data transfer, and it is not possible to take exclusive control of the system for DAC and ADC transfers. In these situations, use I/O block transfers within an interrupt handler. The REP OUTSB instruction of the 80x86 family transfers data from memory to an I/O port specified by the DX register. The REP INSB instruction is the complementary function. Use ES1869 port Audio\_Base+Fh for block transfers.

I/O transfers to FIFO are nearly identical to the DMA process, except that an I/O access to port Audio\_Base+Fh replaces the DMA cycle. For details about programmed I/O operation see "Extended Mode Programmed I/O Operation" on page 51.

### DMA Modes

Extended mode DMA supports both Normal and Auto-Initialize mode. In addition Normal mode and Auto-Initialize mode both support Single and Demand transfer modes.

### Single Transfer

One byte is transferred per DMA request.

### Demand Transfer

To reduce the number of DMA requests necessary to make a transfer, two or four bytes are transferred per DMA request (DRQ). Using Demand transfer enables multiple DMA acknowledges for each DMA request.

For a description of DMA mode including Normal DMA mode and Auto-Initialize DMA mode see "DMA Modes" on page 13.

### Extended Mode Audio 1 Controller Registers

The following registers control operation of the first audio channel in Extended mode:

Table 2 Extended Mode Audio 1 Controller Registers

| Address | Name                                               |

|---------|----------------------------------------------------|

| A1h     | Audio 1 Sample Rate Generator register             |

| A2h     | Audio 1 Filter Clock Divider register              |

| A4h     | Audio 1 Transfer Count Reload register – low byte  |

| A5h     | Audio 1 Transfer Count Reload register – high byte |

| B1h     | Legacy Audio Interrupt Control register            |

| B2h     | Audio 1 DRQ Control register                       |

| B4h     | Input Volume Control register                      |

| B5h     | Audio 1 DAC Direct Access register – low byte      |

| B6h     | Audio 1 DAC Direct Access register – high byte     |

| B7h     | Audio 1 Control 1 register                         |

| B8h     | Audio 1 Control 2 register                         |

| B9h     | Audio 1 Transfer Type register                     |

## Data Transfers Using the Second Audio Channel

The second audio channel is programmed using mixer registers 70h through 7Dh. The commands written to the mixer registers are written to the chip through ports Audio\_Base+4h and Audio\_Base+5h.

14

**DIGITAL AUDIO**

DMA mode is used when programming the second audio channel for transfers:

- DMA modes

- Normal (Single or Demand transfer)

- Auto-Initialize (Single or Demand transfer)

In addition, both DMA Normal mode and DMA Auto-Initialize mode use Single or Demand transfer modes.

### **DMA Modes**

DMA under the second audio channel supports both Normal and Auto-Initialize mode. In addition, Normal mode and Auto-Initialize mode both support Single and Demand transfer modes.

For a description of DMA mode including Normal DMA mode and Auto-Initialize DMA mode, see "DMA Modes" on page 13.

For a description of Single and Demand transfer modes, see "DMA Modes" on page 14.

### Audio 2 Related Mixer Registers

The following registers control DMA operations for the second audio channel:

Table 3 Audio 2 Related Mixer Registers

| Address | Name                                               |

|---------|----------------------------------------------------|

| 70h     | Audio 2 Sample Rate register                       |

| 71h     | Audio 2 Mode register                              |

| 72h     | Audio 2 Filter Clock Rate register                 |

| 74h     | Audio 2 Transfer Count Reload register - low byte  |

| 76h     | Audio 2 Transfer Count Reload register – high byte |

| 78h     | Audio 2 Control 1 register                         |

| 7Ah     | Audio 2 Control 2 register                         |

| 7Ch     | Audio 2 DAC Volume Control register                |

## External DMA Sharing with Audio DMA

It is possible for an external DMA device to share a DMA channel with audio DMA if they do not operate at the same time, and if the respective Windows drivers can communicate with each other. In this case, the external DMA device does not request an audio channel in its resource data. Instead, the Windows driver writes to the PnP DMA register of the appropriate device to assign it to the same DMA channel as one of the two audio channels.

Bits 4:2 of Vendor-Defined Card-Level register 26h can be used to mask any of the three DMA sources (audio 1, audio 2, and external). Use masking when DMA channels are shared to be sure that only one device has access to a given DMA channel at one time.

## **DRQ Latch Feature**

DRQ latching is enabled when bit 7 of PnP Vendor-Defined Card-Level register 25h is high.

If this feature is enabled, each of the four audio DRQs is latched high until one of the following occurs:

- A DACK low pulse occurs while DRQ is low or goes low due to a DACK pulse.

- A hardware reset occurs.

- 8-16 milliseconds elapse while DRQ is low.

## First DMA Channel CODEC

The CODEC of the first audio channel cannot perform stereo DAC and ADC simultaneously. It can either be a stereo DAC, a stereo ADC, or a mono CODEC. After reset, the CODEC is set up for DAC operations. Any ADC command causes a switch to the ADC "direction," and any subsequent DAC command switches the converter back to the DAC "direction."

The DAC output is filtered and sent to the mixer. After reset, input to the mixer from the first audio channel DAC is muted to prevent pops. The ES1869 maintains a status flag to determine if the input to the mixer from the first audio channel DAC is enabled or disabled. Command D8h returns the status of the flag (0h=disabled and FFh=enabled). Use command D1h to enable input to the mixer from the first audio channel DAC and command D3h to disable the input.

To play a new sound without resetting beforehand, when the status of the analog circuits is not clear, mute the input to the mixer with command D3h, then set up DAC direction and level using the direct-to-DAC command:

10h + 80h

Wait 25 milliseconds for the analog circuitry to settle before enabling the voice channel with command D1h.

Pop sounds may still occur if the DAC level was left at a value other than mid-level (code 80h on an 8-bit scale) by the previous play operation. To prevent this, always finish a DAC transfer with a command to set the DAC level to mid-range:

10h + 80h

16

**INTERRUPTS**

## **INTERRUPTS**

There are seven interrupt sources in the ES1869, shown in Table 4.

### Table 4 ES1869 Interrupt Sources

| Interrupt Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Audio 1          | An interrupt used for the first DMA channel (Sound Blaster compatible DMA, Extended mode DMA, and Extended mode programmed I/O), as well as Sound Blaster-compatible MIDI receive. Controller register B1h controls use of this interrupt for Extended mode DMA and programmed I/O. This interrupt request is cleared by hardware or software reset, or an I/O read from port Audio_Base+0Eh. The interrupt request can be polled by reading from port Audio_Base+0Ch. The Audio 1 interrupt is assigned to an interrupt channel by PnP register 70h of LDN 1.                                                                                                                                                       |

| Audio 2          | An optional interrupt for the second DMA channel. The ES1869 can operate in full-duplex mode using two DMA channels. However, since the second DMA channel must share the same sample rate as the first DMA channel, it is not necessary to use a separate interrupt for the second DMA channel. The Audio 2 interrupt is masked by bit 6 of mixer register 7Ah. It can be polled and cleared by reading or writing bit 7 of register 7Ah. This interrupt is assigned to an interrupt channel by PnP register 72h of LDN 1.                                                                                                                                                                                          |

| Hardware Volume  | Hardware volume activity interrupt. This interrupt occurs when one of the three hardware volume controls changes state. Bit 1 of mixer register 64h is the mask bit for this interrupt. The interrupt request can be polled by reading bit 3 of register 64h. The interrupt request is cleared by writing any value to register 66h. The Hardware Volume interrupt is assigned to an interrupt channel by PnP register 27h. Typically this interrupt, if used, is shared with an audio interrupt.                                                                                                                                                                                                                    |

| MPU-401          | The MPU-401 interrupt occurs when a MIDI byte is received. It goes low when a byte is read from the MIDI FIFO and goes high again quickly if there are additional bytes in the FIFO. The interrupt status is the same as the Read-Data-Available status flag in the MPU-401 status register. The MPU-401 interrupt is masked by bit 6 of mixer register 64h. This interrupt is assigned to an interrupt channel in one of two ways. If the MPU-401 is part of the audio device, then PnP register 28h is used to assign the MPU-401 interrupt. If the MPU-401 is its own logical device, it can also be assigned to an interrupt by PnP register 70h of LDN 3. Both these methods access the same physical register. |

| CD-ROM           | The source of the CD-ROM interrupt is the input pin CDIRQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Modem            | The source of the Modem interrupt is the input pin MMIRQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| General-Purpose  | The source of the General-Purpose interrupt is the input pin GPI. If GPI is used for a DMA request for the CD-ROM, Modem, or General-Purpose device, then this pin cannot be used as a general-purpose device interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Interrupt sources are mapped to one of the six interrupt output pins through the PnP registers. Zero, one, or more interrupts can map to any given pin. Each PnP pin is assigned to an ISA interrupt channel number by Vendor-Defined Card-Level PnP registers 20h, 21h, and 22h. These registers are automatically loaded from the 8-byte header in the PnP configuration data.

Each interrupt pin can be in either an active or high-impedance state.

If a given interrupt pin has one or more sources assigned to it, and one or more of those sources is activated (register 30h, bit 0), then the interrupt pin is active; that is, it always drives high or low. An exception is the Modem interrupt, which can be deactivated if input MMIEB is high or if the Modem device is not active. Each interrupt also has one or more mask bits that are AND'ed with the interrupt request.

## Interrupt Status Register

Port Config\_Base+6h of the configuration device can be read to quickly find out which ES1869 interrupt sources are active. The bits are:

| Table 5 | Interrupt Status | Bits in Config_ | _Base+6h |

|---------|------------------|-----------------|----------|

|---------|------------------|-----------------|----------|

| Bit | Description                                                               |

|-----|---------------------------------------------------------------------------|

| 0   | Audio 1 interrupt request                                                 |

| 1   | Audio 2 interrupt request AND'ed with bit 6 of mixer register 7Ah         |

| 2   | Hardware volume interrupt request AND'ed with bit 1 of mixer register 64h |

| 3   | MPU-401 receive interrupt request AND'ed with bit 6 of mixer register 64h |

| 4   | CDIRQ input pin                                                           |

| 5   | MMIRQ input pin AND'ed with inverse of MMIEB input                        |

| 6   | GPI input pin                                                             |

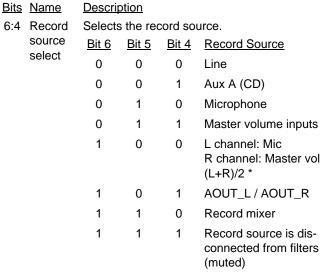

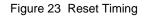

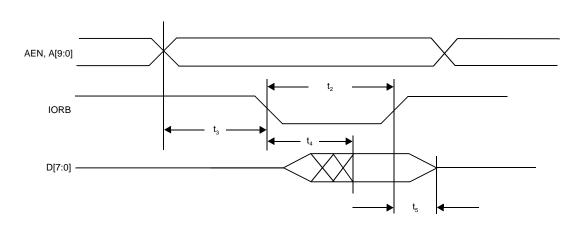

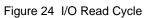

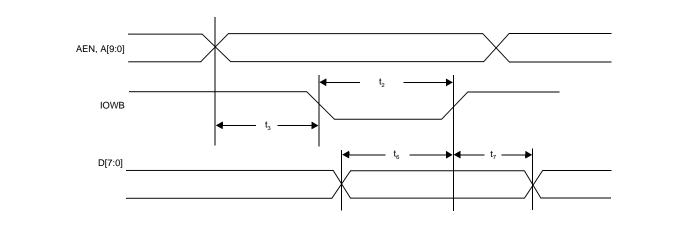

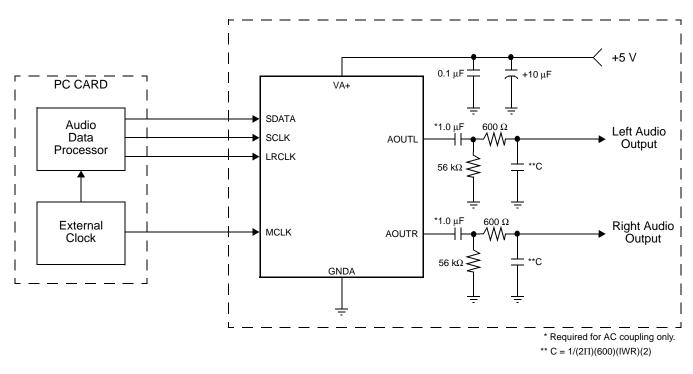

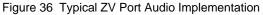

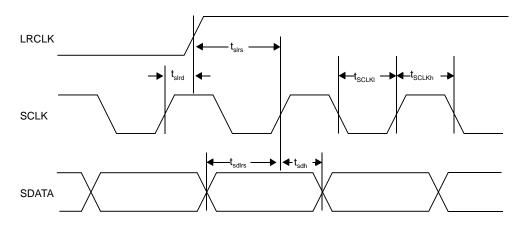

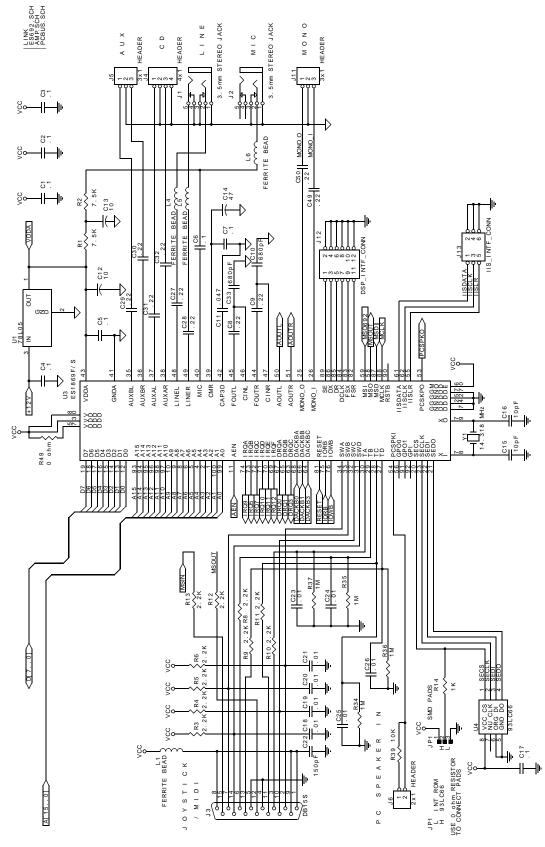

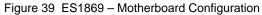

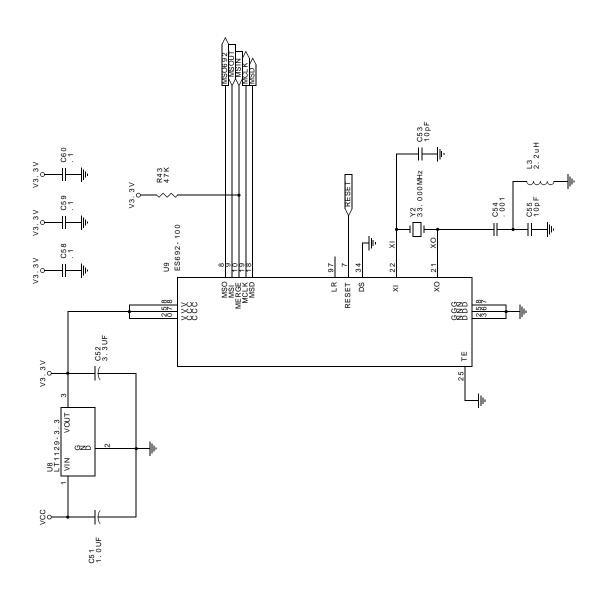

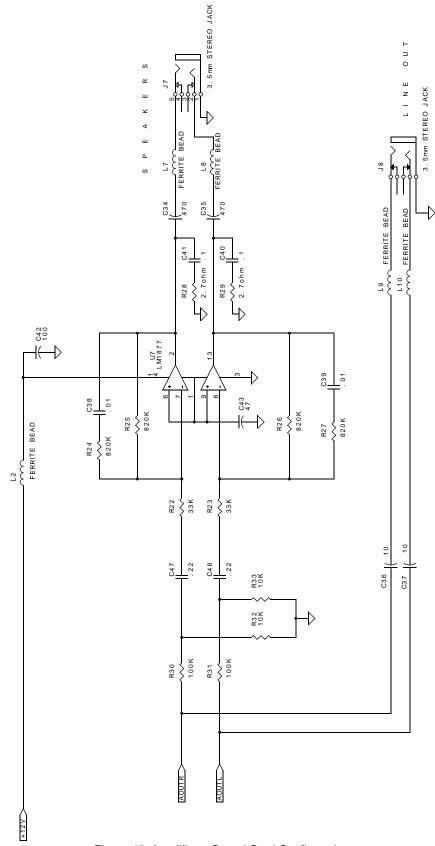

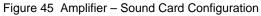

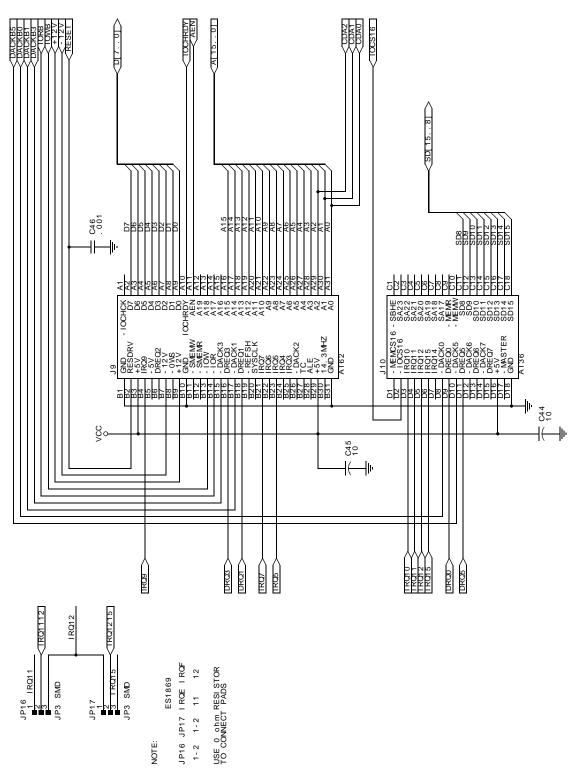

## Interrupt Mask Register